L'illusione dello Spazio Infinito

Alla base, la memoria virtuale riguarda la creazione di un'illusione - l'illusione di avere più memoria di quanta ne esista fisicamente. Ma come funziona questo trucco magico?

Entrano in scena: le Tabelle delle Pagine

Le tabelle delle pagine sono gli eroi non celebrati della gestione della memoria. Agiscono come una mappa, traducendo tra l'immensa distesa di indirizzi virtuali e il limitato regno della memoria fisica. Ecco una visione semplificata di come funzionano:

struct PageTableEntry {

uint32_t physical_page_number : 20;

uint32_t present : 1;

uint32_t writable : 1;

uint32_t user_accessible : 1;

uint32_t write_through : 1;

uint32_t cache_disabled : 1;

uint32_t accessed : 1;

uint32_t dirty : 1;

uint32_t reserved : 5;

};

Ogni voce nella tabella delle pagine corrisponde a una pagina nella memoria virtuale, tipicamente di 4KB. Quando un programma tenta di accedere alla memoria, la CPU utilizza la tabella delle pagine per scoprire dove quella memoria risiede effettivamente nella RAM fisica.

Il Costo della Traduzione

Ma ecco il problema: tradurre gli indirizzi attraverso le tabelle delle pagine è lento. Molto lento. Stiamo parlando di una lentezza paragonabile a guardare la vernice che si asciuga. Per ogni accesso alla memoria, la CPU dovrebbe eseguire più ricerche in memoria solo per capire dove si trova effettivamente il dato. Ed è qui che entra in gioco il nostro prossimo protagonista...

TLB: I Demoni della Velocità nella Traduzione degli Indirizzi

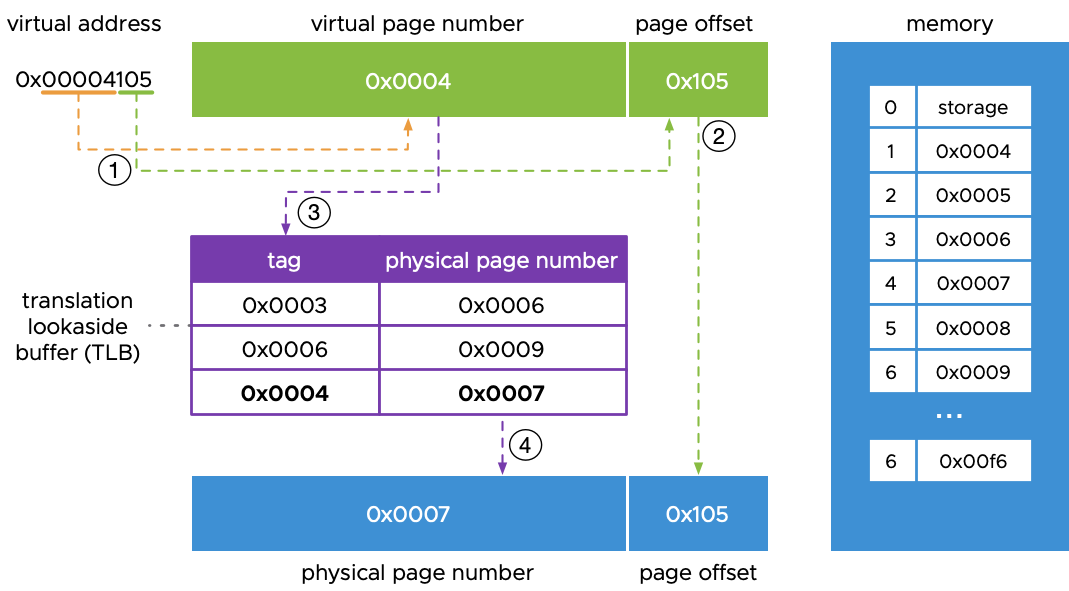

I Translation Lookaside Buffers, o TLB, sono il nitro nel motore della nostra memoria virtuale. Sono piccole e veloci cache che memorizzano le traduzioni recenti dagli indirizzi virtuali a quelli fisici.

Pensa ai TLB come alla memoria a breve termine del tuo cervello per le direzioni. Invece di tirare fuori una mappa (tabella delle pagine) ogni volta che vuoi andare da qualche parte, ricordi semplicemente il percorso se ci sei stato di recente.

Come i TLB Fanno la loro Magia

Ecco un pseudocodice semplificato di come potrebbe operare un TLB:

def access_memory(virtual_address):

if virtual_address in TLB:

physical_address = TLB[virtual_address]

return fetch_data(physical_address)

else:

physical_address = page_table_lookup(virtual_address)

TLB[virtual_address] = physical_address

return fetch_data(physical_address)

Questo semplice meccanismo accelera notevolmente l'accesso alla memoria. Infatti, le CPU moderne possono avere tassi di successo superiori al 99% sui loro TLB, il che significa che 99 accessi alla memoria su 100 non devono toccare affatto le lente tabelle delle pagine!

Il Lato Oscuro: Mancanze del TLB e Thrashing

Ma cosa succede quando il TLB non riesce a trovare una traduzione? Questo è noto come una mancanza del TLB, ed è divertente quanto trovare un bug nel codice di produzione alle 16:59 di un venerdì.

Quando si verifica una mancanza del TLB, la CPU deve:

- Esaminare le tabelle delle pagine per trovare la traduzione corretta

- Aggiornare il TLB con la nuova traduzione

- Ritentare l'accesso alla memoria

Questo processo può essere dolorosamente lento, specialmente se accade frequentemente. Quando il tuo programma inizia a sperimentare molte mancanze del TLB, le prestazioni possono crollare più velocemente di un pallone di piombo. Questa condizione è nota come thrashing del TLB, ed è l'incubo delle applicazioni sensibili alle prestazioni.

Evitare il Thrash

Per mantenere i tuoi programmi in esecuzione senza intoppi, considera questi suggerimenti:

- Usa dimensioni di pagina più grandi quando appropriato (pagine enormi in Linux, pagine grandi in Windows)

- Ottimizza i tuoi schemi di accesso alla memoria per la località

- Fai attenzione alla dimensione del tuo set di lavoro

Ricorda: un TLB felice è un programma performante!

Oltre le Basi: Tecniche Avanzate di Memoria Virtuale

Man mano che ci addentriamo più a fondo nel mondo della memoria virtuale, incontriamo alcune tecniche avanzate affascinanti:

Tabelle delle Pagine Invertite

Le tabelle delle pagine tradizionali possono consumare molta memoria, specialmente nei sistemi a 64 bit. Le tabelle delle pagine invertite cambiano le carte in tavola, utilizzando una tabella hash per mappare le pagine fisiche agli indirizzi virtuali. Questo può ridurre significativamente il sovraccarico di memoria delle tabelle delle pagine, a costo di tempi di ricerca potenzialmente più lunghi.

Tabelle delle Pagine Multilivello

Per gestire gli ampi spazi di indirizzi dei sistemi moderni, le tabelle delle pagine multilivello suddividono il processo di traduzione in fasi. Ad esempio, un tipico sistema x86-64 potrebbe utilizzare quattro livelli di tabelle delle pagine:

CR3 → PML4 → PDP → PD → PT → Pagina Fisica

Questo approccio gerarchico consente un uso efficiente della memoria e una gestione flessibile della memoria.

ASID: Cambio di Contesto Senza il Flush

Gli Address Space Identifiers (ASID) sono un trucco intelligente utilizzato da alcune architetture per evitare di svuotare il TLB ad ogni cambio di contesto. Etichettando le voci del TLB con un ASID, la CPU può mantenere le traduzioni di più processi nel TLB contemporaneamente.

struct TLBEntry {

uint64_t virtual_page_number;

uint64_t physical_page_number;

uint16_t asid;

// ... altri flag

};

Questo può migliorare significativamente le prestazioni nei sistemi con frequenti cambi di contesto.

Il Futuro della Memoria Virtuale

Man mano che spingiamo i confini dell'informatica, la memoria virtuale continua a evolversi. Alcuni sviluppi entusiasmanti all'orizzonte includono:

- Gestione della Memoria Eterogenea: Con l'aumento dei sistemi che combinano diversi tipi di memoria (DRAM, NVRAM, HBM), i sistemi di memoria virtuale si stanno adattando per gestire queste risorse diverse in modo efficiente.

- Camminate delle Tabelle delle Pagine Assistite dall'Hardware: Alcune CPU moderne includono hardware dedicato per eseguire le camminate delle tabelle delle pagine, riducendo ulteriormente l'impatto delle mancanze del TLB sulle prestazioni.

- Prefetching Guidato dall'Apprendimento Automatico: I ricercatori stanno esplorando l'uso di tecniche di apprendimento automatico per prevedere i modelli di accesso alla memoria e prefetchare le pagine nel TLB.

Conclusione: La Spina Dorsale Invisibile dell'Informatica Moderna

La memoria virtuale, con la sua intricata danza di tabelle delle pagine e TLB, forma la spina dorsale invisibile dell'informatica moderna. È una testimonianza dell'ingegnosità degli scienziati e degli ingegneri informatici, che creano l'illusione di spazi di memoria vasti e contigui a partire da risorse fisiche frammentate.

La prossima volta che il tuo programma viene eseguito, pensa al complesso meccanismo che lavora dietro le quinte, traducendo i tuoi spensierati indirizzi virtuali in realtà fisica. E ricorda, nel mondo della memoria virtuale, nulla è come sembra - ma è proprio questo che la rende così potente.

"Nell'informatica, ci troviamo sulle spalle dei giganti - e quei giganti stanno su una molto intelligente implementazione della memoria virtuale." - Anonimo Bit Wrangler

Ora vai avanti e alloca memoria con abbandono sconsiderato - il tuo sistema di memoria virtuale ti copre le spalle!